Il doit être associé à un récepteur infra-rouge type TL1838 ou équivalent.

Il peut être alimenté de 3 à 5V DC.

Une led visualise la réception de la trame.

La lecture I2C est fonctionnelle à 100khz et à 400khz.

La consommation au repos est négligeable car le circuit est en mode power down (technologie nanowatt des PIC 16F).

Elle est de 4mA environ lors de la réception de trame ou lecture I2C.

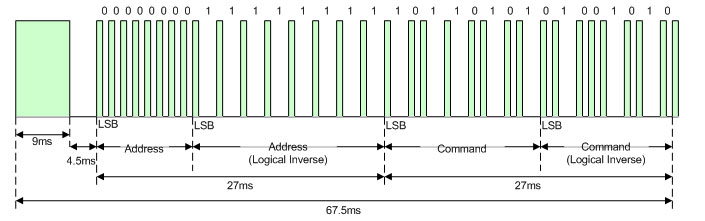

Trame NEC 32 bits

Lors d'une réception infra-rouge , le circuit teste en interne l'adresse avec son inverse et la commande avec son inverse.

Si l'égalité de chaque octet avec son inverse est vérifiée, INT prend la valeur 0 pour demander la lecture I2C.

Dans le cas contraire , INT reste à 1 et la trame IR est ignorée.

Ainsi, il n'est pas pertinent (et donc inutile) de fournir les octets inverses lors de la lecture I2C.

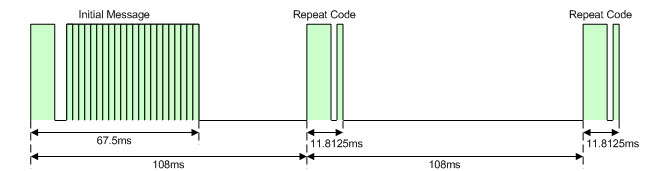

Cas du repeat : si la lecture I2C est effective dès le passage de INT à 0, le circuit provoque une nouvelle interruption toutes les 108ms lors de la réception des codes de répétition.

Le circuit sera raccordé à un master I2C qui pourra venir lire les 3 octets reçus par ce dernier lorsque INT passe à 0.

La lecture I2C correcte des 3 octets provoque la remontée de INT à 1.

Si le master I2C a lu la trame infra-rouge avant l'arrivée du premier repeat (108ms),

une nouvelle interruption est générée avec le passage de INT à 0 lors du repeat.

Dans tous les cas, la lecture I2C devra être effective avant l'appui sur une nouvelle touche.

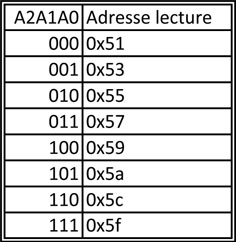

Le circuit peut prendre plusieurs adresses I2C selon les niveaux appliqués sur les broches A0 A1 A2.

La prise en compte de ces entrées intervient seulement à la mise sous tension du circuit.

Adresse lecture sur 8 bits (DEVICE ADDRESS)

Adresse lecture sur 8 bits (DEVICE ADDRESS)

Le bit de poids 0 est le bit R/W de l’adresse I2C, toujours=1 car le cicuit ne supporte que la lecture.

Info Telecommandes

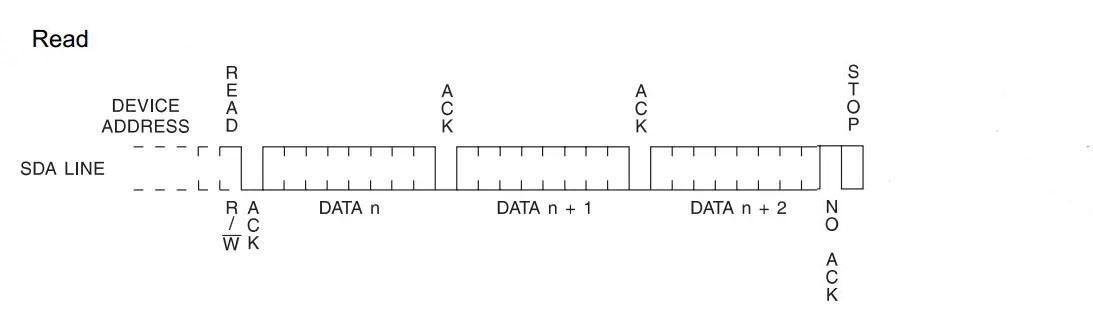

Lecture I2C

Le master I2C génère un start.

Le master adresse le circuit RECNECI2C avec l’adresse sur 8 bits correspondant à A2A1A0 (de 51H à 5FH) qui acquitte son adresse en lecture.

Le master récupère 3 octets (envoyés par le RECNECI2C) en acquittant les 2 premiers , sans acquitter le dernier, puis génère un stop.

Octet DATA n : adresse NEC|Octet DATA n+1: commande NEC | Octet DATA n+2 : 00 si première et nouvelle réception infra-rouge, 0xFF si trame IR issue du repeat.

Exemple : Appui sur touche télécommande , INT passe a 0, le master I2C lit :"00 02 00", le doigt reste en appui 160ms, INT repasse à 0, le master I2C lit "00 02 FF"...

Si le doigt reste en appui 230ms , INT repasse à 0, le master I2C effectuera une nouvelle lecture "00 02 FF" et ainsi de suite...

Ainsi, c'est le troisième octet qui signale un nouvel appui sur une touche lorsqu'il vaut 0.

Les réceptions avec le troisième octet à 0xff signifient que le doigt est resté en appui sur la touche correspondant aux valeurs reçues précédemment déjà lues,

indiquant ainsi que les 2 octets associés sont issus du repeat.

Routines master PIC 16F MSSP pour lire ce circuit en I2C:

-I2CMaster.h

-I2CMaster.c

Les circuits sont disponibles en 2 formats :

-DIP14

-SOP14

Le circuit RECNECI2C est fourni de façon pérenne par la société AIXIST .

https://aixist.fr/index.php?page=contact

Prise de contact par le formulaire

Renseignements techniques :

electro8051@yahoo.fr