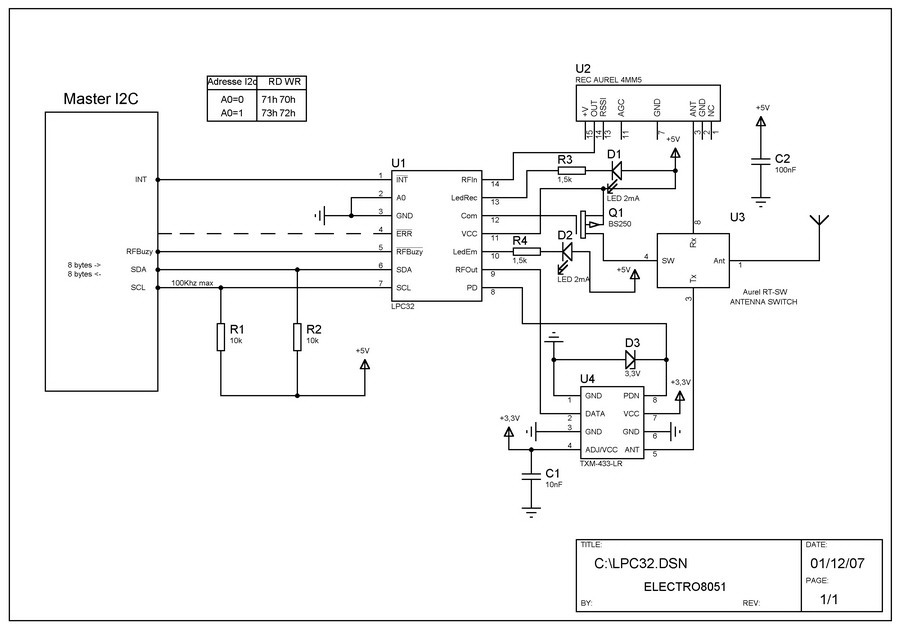

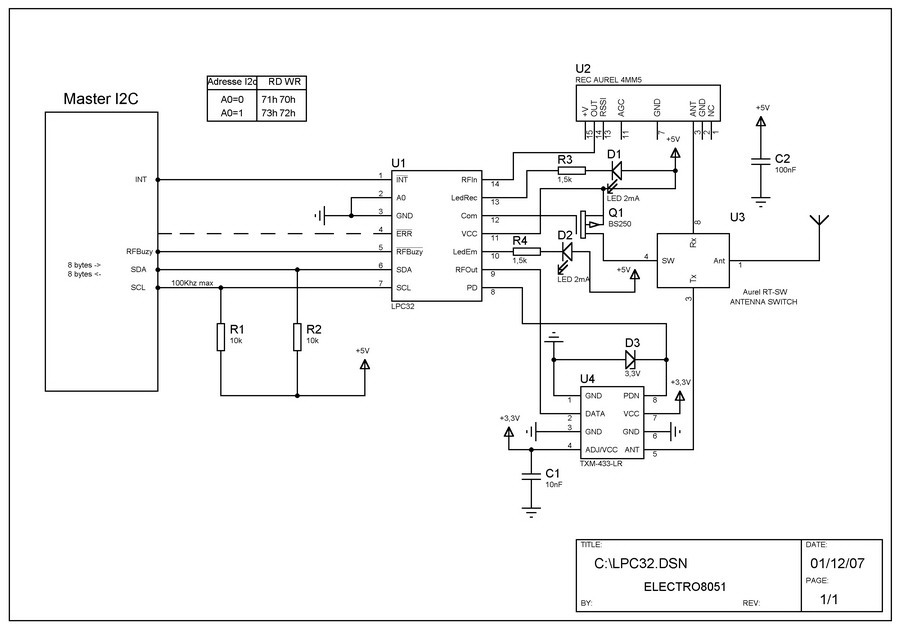

Le circuit

LPC32 est un microcontrôleur OTP Philips 14 broches (P87LPC760BN) programmé pour

gérer une transmission radio à codage PWM à travers un

bus I2C.

Il

s'alimente avec une tension continue comprise entre 3 et 5V.

Sa base de temps

se contente du circuit RC interne,de même, le reset est effectué sans

composant

externe.La fonction décodage PWM (réception) se synchronise sur l'emetteur à

chaque envoi de trame , la possible dérive du timing est ainsi prise en compte.

La transmission

radio s'effectue en half duplex, 8 octets+1 octet CRC sont envoyés/reçus

vers/de un autre LPC32.

Le LPC32 ne traitant que le niveau 1 de la transmission,

les éventuels éléments de protocole sont à intégrer

par l'utilisateur (système d'adressage)

dans les 8 octets transportés.

Le circuit peut toutefois être utilisé en émission ou

réception

uniquement dans le cas d'une transmission unidirectionnelle.Dans ce cas,

seul l'émetteur

ou le récepteur radio sera raccordé

au circuit.

Le schéma présenté montre toute les possibilités

(transmission bidirectionnelle,switch d'antenne et gestion du Power down

de l'émetteur).

1.Emission

Le master

I2C envoie 8 octets (obligatoirement 8 octets) avec le bit0 de l'adresseI2C=0

Le LPC32 acquitte les 8 octets,calcule le CRC et procéde à la

transmission radio de 9 octets (8 octets data + 1 octet CRC).

Le début de la transmission radio est signifiée au master par le signal RFBusy

qui passe à 0,

ce

niveau logique demeurant à l'état bas tant que la transmission n'est pas terminée.

La transmission radio s'effectue en codage PWM,une séquence de préambule

est envoyée

au préalable afin de permettre au récepteur de se synchroniser

malgré le bruit ambiant.

Le temps total d'émission d'une trame radio est de 98,4 mS.

La led raccordée sur la broche LedEm s'éclaire pendant l'émission

de la trame.

2.Réception

La

réception

d'une trame radio est marquée par le signal RFBuzy qui prend la valeur

0 jusqu'à la

fin de la trame. La réception

d'une trame complète et sans erreur provoque le passage à 0

du signal INT.

Il appartient au master I2C de procéder à la lecture des 8 octets reçus

au plus tôt.

La fin de la lecture I2C des 8 octets provoque la remontée

de INT.

La réception d'une trame complète avec une erreur de CRC provoque uniquement

le passage à 0 du signal ERR.Ce signal est remis à 1 dès qu'une trame est

reçue complète et sans erreur de CRC.La gestion de ce signal est facultative.

Le circuit permet de gérer un switch d'antenne grâce à la

sortie Com.Ce switch est bien sûr facultatif.

Le circuit permet également de gérer le signal Power down de l'émetteur (s'il

en est pourvu).

L'utilisation de cette sortie est également facultative.

La led raccordée sur la brochee LedRec s'éclaire quand le LPC32

interprête des informations reçues par le récepteur.

|

Adressage du LPC32 en WR avec adresse I2C 70h

SCL

SDA |

|

Adressage du LPC32 en RD avec adresse

I2C 71h

SCL

SDA |

Important:

Le LPC32 comporte un dispositif de stretching

interne qui tire le signal SCL à l'état bas en cas d'occupation

interne du circuit.

C'est le cas dans le graphique précédent pour le bit 6 de SCL de

l'adresse (2° pulse de syncro en partant de la gauche après le start).On

constate que l'état bas entre le premier et le deuxième pulse est

plus large que les états bas entre les autres pulses).

Voir spécifications

du bus I2C page

13 8.3

Conséquence

pour la routine master I2C qui envoie l'octet sur le bus:

La routine master qui vient de fixer SCL à l'état

haut doit venir tester si SCL est effectivement à l'état haut,attendre

si nécessaire que cette condition soit vérifiée et fixer

l'état haut à 5 µS max avec SCL=1 (100khz).

Toute routine I2C master correctement écrite doit fonctionner ainsi afin

de garantir la compatibilité avec tous les circuits I2C et respecter les

spécifications I2C.

| Schéma

format PDF |

|

| Routine I2C

maître en assembleur pour 8051 |

I2C_A51.TXT |

| Fichier INC

associé pour 8051 de base |

8051.INC |

| Routines en

C pour utiliser le LPC32 |

LPC32_C.TXT |

| |

|

Si

vous souhaitez mettre en oeuvre le LPC32 Me contacter